# Trilinear

# Display Stream Compression

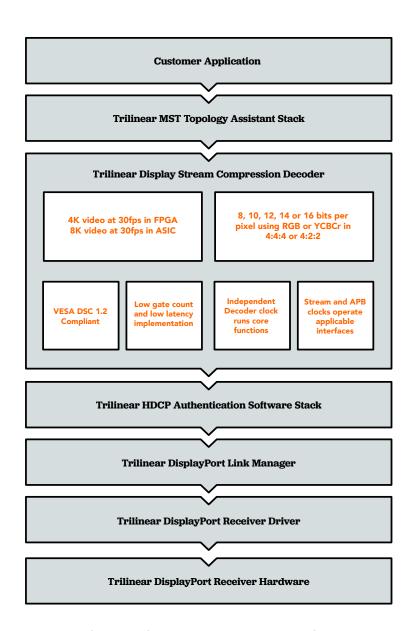

### **DSC DECODER**

The Trilinear Technologies Display Stream Compression (DSC) Decoder core offers real-time decompression of high-definition streams with resolutions from 480 to 8K. The core supports 8, 10, 12, 14 or 16 bits per pixel using either RGB or YCbCr in 4:4:4 or 4:2:2 format. The DSC Decoder core integrates industry standard interfaces for host configuration and control, data input, and video output.

### AT A GLANCE:

- Capable of decoding up to 4K video at 30fps in FPGA and 8K video at 30fps in ASIC applications

- Low gate count and low latency implementation

- Three clock domains:

- Stream and APB clocks operate the applicable interfaces

- Independent decoder clock runs the core functions

- Fully compliant with the VESA DSC

1.2a standard

- Uses synchronus design techniques and a technology abstraction layer for internal SRAM buffers

- Allows for migration from FPGA or FPGA prototype to ASIC with no functional changes to the core

- Completely pipelined; can be stalled as necessary to properly manage input and output rates

### Host

32-bit AMBA Peripheral Bus 4 (APB) slave interface for programming and control. All internal configuration and status registers are accessible from the APB interface.

### Input

AXI4-Stream Protocol interface supports the transfer of encoded data to the core at 2 or 4 bytes per clock cycle.

# **Output**

Parallel streaming interface with end-of-line and top-of-frame indicators.

### Performance & Area

The DSC Decoder implementation includes best-in-class design processes and is efficient in resource usage and operating frequency. The core requires less than 300K gates in the TSMC 28HP process, and a 175MHz core clock performs 4K decode. For detailed information on area and timing, please contact Trilinear Technologies with the specific technology platform required.

Figure 1. Trilinear Display Stream Compression Decoder

# **Delivery & Availability**

The DSC Decoder is currently available as a soft core in one of several configurations for both FPGA and ASIC implementations. The core includes a complete 'C' reference driver, fully documented software API, and stream decoder sample application. Customers may select from off-the-shelf versions of the core or a version with customized interfaces. Custom host processor and memory interfaces may be requested at no additional charge.

The core is also available on the Trilinear Technologies' Cobra Development platform based on the Xilinx Kintex-7 FPGA family. This FPGA-based reference system provides a complete development environment for core evaluation as well as early software development.

# **Verification Testing**

Verification testing for the DSC Decoder is fully compliant with the VESA DSC 1.2a specification; it has been thoroughly validated using the VESA software model as the golden reference. Trilinear Technologies completed extensive interoperability testing with 3rd party reference models and test suites, along with the reference hardware using a variety of shipping encoder products. The core has also been verified in conjunction with the Embedded DisplayPort 1.4b Transmitter design. Hardware validation was performed using eDP-compliant sink devices.

The core ships with a self-checking test bench to illustrate the proper management of the input and output interfaces. The test bench environment is extensible and can be used to implement customer-specific test scenarios.

TRILINEAR TECHNOLOGIES

STANDING THE TEST — EVERY TEST, EVERY TIME.

### **Design Database**

Trilinear Technologies delivers an extensive design database for the DSC Decoder core. The database includes all of the files required to implement the design on multiple platforms, including FPGA and ASIC technologies. In addition to the core implementation files, delivery includes reference software drivers and applications, along with the associated documentation to reduce the amount of time for software development. Files and data include:

- HDL source files for the function design

- HDL source files for block level and top level testing

- Functional specification

- Timing constraints summary document

- Generic SRAM simulation models

- C Reference Driver

Trilinear Technologies offers

the DSC Decoder core either

directly or through a qualified

distribution partner under

several licensing models.

Please contact Trilinear

Technologies for pricing and

additional information:

trilineartech.com